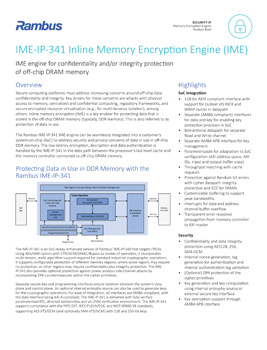

The Rambus IME-IP-341 IME engine can be seamlessly integrated into a customer’s system-on-chip (SoC) to address security and privacy concerns of data in use in off-chip DDR memory. The low latency encryption, decryption and data authentication is handled by the IME-IP-341 in the data path between the processor’s last-level cache and the memory controller connected to off-chip DRAM memory.

Using AES/SM4 ciphers with CTR/GCM/GMAC/Bypass as modes of operation, it incorporates multi-stream, multi-algorithm support required for standard industrial cryptographic operations. The IME-IP-341 also provides optional protection against power analysis side-channel attacks by incorporating DPA countermeasures within the cipher primitives.

Download this brief to:

- Learn about the features of the IME-IP-341 Engine

- See the block diagram

- Review available deliverables

Get the brief by completing the form.